Transformation des Alltags

Gemeinsam die Industrie verändern und Ideen in Innovationen umwandeln.

Wie KI die Instandhaltung in Fabriken verändert

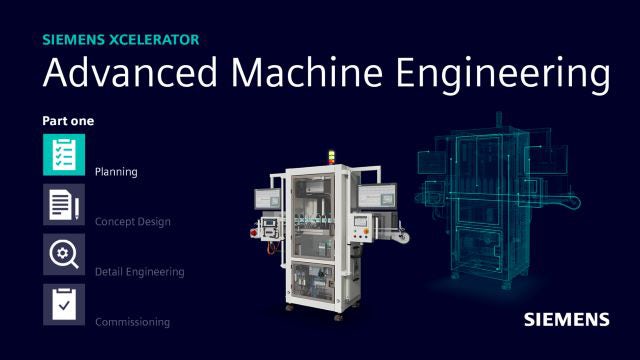

Unser digitaler Zwilling ist die einzige Vertrauensquelle, um intelligente Entscheidungen auf der Grundlage von Daten zu ermöglichen. Nur Siemens verbindet die reale und die digitale Welt zu einem wirklich digitalen Unternehmen.

Nachhaltigkeit

Wir schaffen nachhaltige industrielle Innovationen für eine Welt, in der wir heute und in Zukunft leben wollen, und für eine Branche, die auf diesem Planeten keine Spuren hinterlassen will.

Zukunft der Mobilität

Wir ermöglichen die Zukunft der Mobilität in der Luft, zu Lande und zu Wasser, indem wir zu einer Revolution des Transportwesens beitragen, um das Reisen angenehmer und nachhaltiger zu gestalten.

Additive Fertigung

Wir liefern pragmatische additive Fertigung für Unternehmen jeder Größe. Wir ermöglichen durchgängige Prozesse für die additive Fertigung, um sie einfach, kostengünstig und allgegenwärtig zu machen.

Künstliche Intelligenz

Durch die Nutzung von Big Data ermöglichen unsere KI-Innovationen und -Lösungen eine intelligentere Entscheidungsfindung, mehr Effizienz, eine bessere Qualität und eine schnellere Markteinführung bei gleichzeitiger Erschließung neuer Geschäfte.

Modellbasierter Systementwurf

Unsere integrierte modellbasierte Systemdesign-Methodik (MBSE) vereint alle Bereiche, die für die Entwicklung der heutigen intelligenten Systeme erforderlich sind, und konzentriert sich alle auf die Beschleunigung von Produktinnovationen oder Geschäftserfolgen.

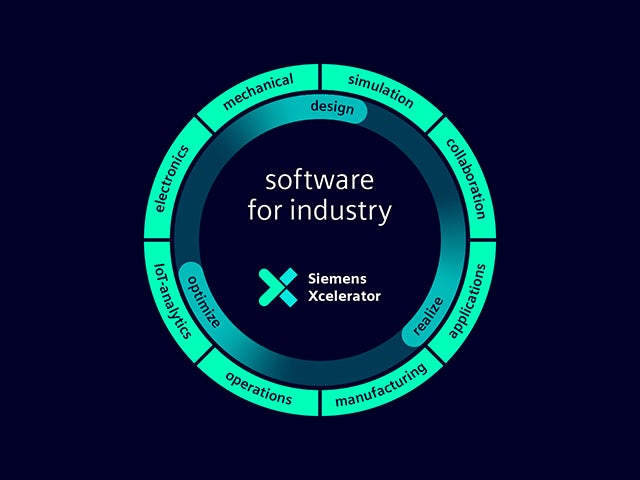

Was braucht es, um ein digitales Unternehmen zu werden?

Surf Loch nutzt die digitalen Technologien von heute, um die Surfindustrie zu revolutionieren. Mit einem kleinen Team von engagierten Ingenieuren nutzten sie Software und Services innerhalb des Siemens Xcelerator-Portfolios, um allen Surfern die Möglichkeit zu geben, die perfekte Welle zu reiten, wann immer sie wollen.

Erfahren Sie mehr über ihre inspirierende digitale Transformation.

Transformation des Alltags

Besuchen Sie unseren Blog, um weitere Informationen über das Siemens Xcelerator Portfolio und Siemens Xcelerator as a Service zu erhalten.